|

|

CLK160 | in |

| | 160 MHz clock used by SUSTEM_TEST for dcfeb prbs test.

|

|

CLK40 | in |

| | 40 MHz "fastclk" used for numerous purposes by VMEMON, VMECONFREGS, SYSTEM_TEST, COMMAND_MODULE, and SPI_CTRL

|

|

CLK10 | in |

| | 10 MHz "midclk" currently unused

|

|

CLK2P5 | in |

| | 2.5 MHz "slowclk" used for most slow control logic

|

|

CLK1P25 | in |

| | 1.25 MHz "slowclk" used by CFEBJTAG, SYSTEM_MON, and LVDBMON

|

|

VME_DATA_IN | in ( 15 downto 0 ) |

| | VME data input signal used by all modules.

|

|

VME_DATA_OUT | out ( 15 downto 0 ) |

| | VME data output signal multiplexed from all modules.

|

|

VME_GAP_B | in |

| | VME geographical address (VME slot) parity. Checked by COMMAND_MODULE.

|

|

VME_GA_B | in ( 4 downto 0 ) |

| | VME geographical address signal. Checked by COMMAND_MODULE.

|

|

VME_ADDR | in ( 23 downto 1 ) |

| | VME address (command). Processed by COMMAND_MODULE and relevant bits passed to other modules as 'cmd'.

|

|

VME_AM | in ( 5 downto 0 ) |

| | VME address modifier. Checked by COMMAND_MODULE.

|

|

VME_AS_B | in |

| | VME address strobe. Checked by COMMAND_MODULE.

|

|

VME_DS_B | in ( 1 downto 0 ) |

| | VME data strobe. Checked by COMMAND_MODULE and passed to other modules as 'strobe'.

|

|

VME_LWORD_B | in |

| | VME data word length. Checked by COMMAND_MODULE.

|

|

VME_WRITE_B | in |

| | VME write/read signal used by all modules.

|

|

VME_IACK_B | in |

| | VME interrupt acknowledge. Checked by COMMAND_MODULE.

|

|

VME_BERR_B | in |

| | VME bus error indicator. Checked by COMMAND_MODULE.

|

|

VME_SYSFAIL_B | in |

| | VME system failure indicator. Checked by COMMAND_MODULE.

|

|

VME_DTACK_B | out |

| | VME data acknowledge. Output is the not of the OR of the DTACK signals from each module.

|

|

VME_OE_B | out |

| | VME output enable. Generated by COMMAND_MODULE.

|

|

VME_DIR_B | out |

| | VME input/output direction. Generated by COMMAND_MODULE.

|

|

DCFEB_TCK | out ( NCFEB downto 1 ) |

| | DCFEB JTAG test clock signal from CFEBJTAG module.

|

|

DCFEB_TMS | out |

| | DCFEB JTAG test mode select signal from CFEBJTAG module.

|

|

DCFEB_TDI | out |

| | DCFEB JTAG test data in signal from CFEBJTAG module.

|

|

DCFEB_TDO | in ( NCFEB downto 1 ) |

| | DCFEB JTAG test data out signal to CFEBJTAG module.

|

|

DCFEB_DONE | in ( NCFEB downto 1 ) |

| | DCFEB programming done signal. Monitored by VMEMON module.

|

|

DCFEB_INITJTAG | in |

| | Signal generated by top module when DCFEBs finish programming. Used by CFEBJTAG to reset DCFEB JTAG state machine.

|

|

DCFEB_REPROG_B | out |

| | DCFEB reprogram signal generated by VMEMON module.

|

|

LVMB_PON | out ( 7 downto 0 ) |

| | Power-on signals to LVMB. Set by LVDBMON module.

|

|

PON_LOAD_B | out |

| | Signal to write LVMB_PON to LVMB. Generated by LVDBMON module.

|

|

PON_OE | out |

| | Output enable for LVMB_PON, fixed to 1.

|

|

R_LVMB_PON | in ( 7 downto 0 ) |

| | Power-on signals from LVMB. Monitored by LVDBMON.

|

|

LVMB_CSB | out ( 6 downto 0 ) |

| | LVMB monitor ADC SPI chip select signal. Generated by LVDBMON.

|

|

LVMB_SCLK | out |

| | LVMB monitor ADC SPI clock signal. Generated by LVDBMON.

|

|

LVMB_SDIN | out |

| | LVMB monitor ADC SPI input signal. Generated by LVDMBMON.

|

|

LVMB_SDOUT | in |

| | LVMB monitor ADC SPI output signal. Monitored by LVDBMON.

|

|

OTMB | in ( 35 downto 0 ) |

| | OTMB data signals, used by SYSTEM_TEST for OTMB PRBS test.

|

|

RAWLCT | in ( NCFEB - 1 downto 0 ) |

| | OTMB local charged track signals, used by SYSTEM_TEST for OTMB PRBS test.

|

|

OTMB_DAV | in |

| | OTMB data available signal, used by SYSTEM_TEST for OTMB PRBS test.

|

|

OTMB_FF_CLK | in |

| | Unused.

|

|

RSVTD_IN | in ( 7 downto 3 ) |

| | OTMB reserved to DMB output signals, used by SYSTEM_TEST for OTMB PRBS test.

|

|

RSVTD_OUT | out ( 2 downto 0 ) |

| | OTMB reserved to DMB input signals, generated by SYSTEM_TEST for OTMB PRBS test.

|

|

LCT_RQST | out ( 2 downto 1 ) |

| | Local charge track request signal, generated by SYSTEM_TEST for OTMB PRBS test.

|

|

FW_RESET | out |

| | Signal from VMEMON used to generate soft reset.

|

|

L1A_RESET_PULSE | out |

| | Signal from VMEMON used to reset L1A counter.

|

|

OPT_RESET_PULSE | out |

| | Signal from VMEMON used to generate reset to optical firmware.

|

|

TEST_INJ | out |

| | Signal from VMEMON to CALIBTRIG used to generate calibration INJPLS to DCFEBs.

|

|

TEST_PLS | out |

| | Signal from VMEMON to CALIBTRIG used to generate calibration EXTPLS to DCFEBs.

|

|

TEST_BC0 | out |

| | Signal from VMEMON used to generate bunch crossing 0 synchronization signal to DCFEBs.

|

|

TEST_PED | out |

| | Signal from VMEMON that causes OTMB data to be requested for each L1A (pedestal).

|

|

TEST_LCT | out |

| | Signal from VMEMON used to generate an L1A to ODMB_CTRL.

|

|

MASK_L1A | out ( NCFEB downto 0 ) |

| | Signal from VMEMON that masks L1A and L1A matches.

|

|

MASK_PLS | out |

| | Signal from VMEMON that masks DCFEB INJPLS and EXTPLS signals.

|

|

ODMB_CAL | out |

| | Signal from VMEMON that sets calibration mode in TRIGCTRL (L1A generated with each INJPLS).

|

|

MUX_DATA_PATH | out |

| | Signal from VMEMON that selects whether data comes from real boards or is simulated data.

|

|

MUX_TRIGGER | out |

| | Signal from VMEMON that selects if trigger signals (L1A, LCT) are external or from TESTCTRL.

|

|

MUX_LVMB | out |

| | Signal from VMEMON that selects if LVMB communication is to real board or simulated LVMB.

|

|

ODMB_PED | out ( 1 downto 0 ) |

| | Pedestal signal from VMEMON that generates L1A matches for all L1As when enabled.

|

|

ODMB_DATA | in ( 15 downto 0 ) |

| | General data signal to VMEMON for monitoring various signals.

|

|

ODMB_DATA_SEL | out ( 7 downto 0 ) |

| | ODMB_DATA selector signal from VMEMON.

|

|

LCT_L1A_DLY | out ( 5 downto 0 ) |

| | VMECONFREGS register controlling LCT delay in CALIBTRG.

|

|

CABLE_DLY | out range 0 to 1 |

| | VMECONFERGS register controlling delay for DCFEB bound signals (L1A,L1A_MATCH,RESYNC,BC0) in top level.

|

|

OTMB_PUSH_DLY | out range 0 to 63 |

| | VMECONFREGS register controlling delay between OTMBDAV and pushing to the FIFO in TRGCNTRL.

|

|

ALCT_PUSH_DLY | out range 0 to 63 |

| | VMECONFREGS register controlling delay between ALCTDAV and pushing to the FIFO in TRGCNTRL.

|

|

BX_DLY | out range 0 to 4095 |

| | VMECONFREGS register that would be used in counting bunch crossings in CAFIFO, but actually unused.

|

|

INJ_DLY | out ( 4 downto 0 ) |

| | VMECONFREGS register controlling delay for calibration INJPULSE in CALIBTRG.

|

|

EXT_DLY | out ( 4 downto 0 ) |

| | VMECONFREGS register controlling delay for calibration EXTPULSE in CALIBTRG.

|

|

CALLCT_DLY | out ( 3 downto 0 ) |

| | VMECONFREGS register controlling delay for calibration LCT in CALIBTRG.

|

|

ODMB_ID | out ( 15 downto 0 ) |

| | VMECONFREGS register storing unique ODMB ID.

|

|

NWORDS_DUMMY | out ( 15 downto 0 ) |

| | VMECONFREGS register controlling the number of words generated by dummy DCFEBs/ALCT/OTMB.

|

|

KILL | out ( NCFEB + 2 downto 1 ) |

| | VMECONFREGS register controlling which boards (ALCT/OTMB/DCFEBs) should be ignored.

|

|

CRATEID | out ( 7 downto 0 ) |

| | VMECONFREGS register with VME crate ID, used by CONTROL_FSM in packet generation.

|

|

CHANGE_REG_DATA | in ( 15 downto 0 ) |

| | Signals to VMECONFREGS to auto-kill bad boards, new value for KILL.

|

|

CHANGE_REG_INDEX | in range 0 to NREGS |

| | Signals to VMECONFREGS to auto-kill bad boards, will only ever be 7(KILL) or NREGS(none).

|

|

CNFG_DATA_IN | in ( 7 downto 4 ) |

| | SPI data signal from secondary PROM to SPI_INTERFACE.

|

|

CNFG_DATA_OUT | out ( 7 downto 4 ) |

| | SPI data signal to secondary PROM from SPI_INTERFACE.

|

|

CNFG_DATA_DIR | out ( 7 downto 4 ) |

| | SPI data direction signal for secondary PROM from SPI_INTERFACE.

|

|

PROM_CS2_B | out |

| | SPI chip select to secondary PROM from SPI_INTERFACE.

|

|

MGT_PRBS_TYPE | out ( 3 downto 0 ) |

| | DDU/SPY/DCFEB/ALCT Common PRBS type select from SYSTEM_TEST.

|

|

DDU_PRBS_TX_EN | out ( 3 downto 0 ) |

| | DDU PRBS transmitter enable signal from SYSTEM_TEST. Unused.

|

|

DDU_PRBS_RX_EN | out ( 3 downto 0 ) |

| | DDU PRBS receiver enable signal from SYSTEM_TEST to MGT_DDU.

|

|

DDU_PRBS_TST_CNT | out ( 15 downto 0 ) |

| | DDU PRBS length from SYSTEM_TEST to MGT_DDU.

|

|

DDU_PRBS_ERR_CNT | in ( 15 downto 0 ) |

| | DDU PRBS errors reported signal to SYSTEM_TEST from MGT_DDU.

|

|

SPY_PRBS_TX_EN | out ( 0 downto 0 ) |

| | SPY transmitter enable signal from SYSTEM_TEST to MGT_SPY.

|

|

SPY_PRBS_RX_EN | out ( 0 downto 0 ) |

| | SPY receiver enable signal from SYSTEM_TEST to MGT_SPY.

|

|

SPY_PRBS_TST_CNT | out ( 15 downto 0 ) |

| | SPY PRBS length from SYSTEM_TEST to MGT_SPY.

|

|

SPY_PRBS_ERR_CNT | in ( 15 downto 0 ) |

| | SPY PRBS errors reported signal to SYSTEM_TEST from MGT_SPY.

|

|

DCFEB_PRBS_FIBER_SEL | out ( 3 downto 0 ) |

| | Selector for fiber used in DCFEB PRBS test from SYSTEM_TEST. Unused.

|

|

DCFEB_PRBS_EN | out |

| | DCFEB PRBS enable signal from SYSTEM_TEST. Unused.

|

|

DCFEB_PRBS_RST | out |

| | DCFEB PRBS reset signal from SYSTEM_TEST. Unused.

|

|

DCFEB_PRBS_RD_EN | out |

| | DCFEB PRBS read enable signal from SYSTEM_TEST. Unused.

|

|

DCFEB_RXPRBSERR | in |

| | DCFEB PRBS RX error signal. Unused.

|

|

DCFEB_PRBS_ERR_CNT | in ( 15 downto 0 ) |

| | DCFEB PRBS errors reported signal to SYSTEM_TEST from MGT_CFEB.

|

|

SYSMON_P | in ( 15 downto 0 ) |

| | Current monitoring analog signals from ICs to SYSTEM_MON.

|

|

SYSMON_N | in ( 15 downto 0 ) |

| | Current monitoring analog signals from ICs to SYSTEM_MON.

|

|

ADC_CS_B | out ( 4 downto 0 ) |

| | SPI chip select signals from SYSTEM_MON to voltage monitor ADCs.

|

|

ADC_DIN | out |

| | SPI data input signal from SYSTEM_MON to voltage monitor ADCs.

|

|

ADC_SCK | out |

| | SPI clock signal from SYSTEM_MON to voltage monitor ADCs.

|

|

ADC_DOUT | in |

| | SPI data output signal to SYSTEM_MON from voltage monitor ADCs.

|

|

DIAGOUT | out ( 17 downto 0 ) |

| | Debug signal.

|

|

RST | in |

| | Firmware soft reset signal from top level.

|

|

PON_RESET | in |

| | Power-on reset signal from top level, currenly unused.

|

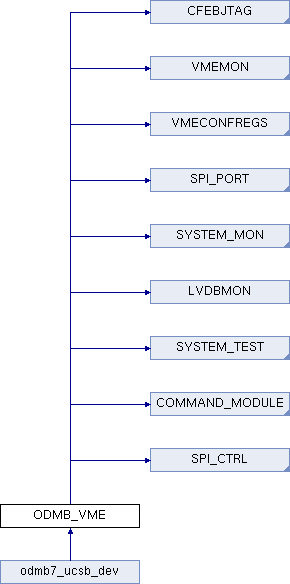

ODMB7 VME (slow control) module.

ODMB7 module that processes slow control commands from the VMEbus backplane This module contains several 'device' submodules dedicated to certain types of commands The commands for device X take the for XYYY. The devices are:

- Device 0 - TESTCTRL - NOT IMPLEMENTED

- Device 1 - CFEBJTAG - generates slow control commands in the JTAG protocol for (x)DCFEBs

- Device 2 - ODMBJTAG - generates slow control commands in the JTAG protocol for the ODMB7 FPGA (Kintex Ultrascale)

- Device 3 - VMEMON - used to monitor various registers, set certain settings, and send reset signals

- Device 4 - VMECONFREGS - used to interact with the configuration and constant registers loaded from nonvolatile memory

- Device 5 - TESTFIFOS - NOT IMPLEMENTED

- Device 6 - SPI_PORT - used to interact with ODMB7 PROM ICs

- Device 7 - SYSTEM_MON - used to measure temperature, currents, and voltages

- Device 8 - LVDBMON - used to interact with LVMB7 board

- Device 9 - SYSTEM_TEST - used to perform communication tests including optical connection to (x)DCFEBs, backplane connection to OTMB, and FED/SPY loopback

1.8.5

1.8.5