|

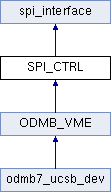

ODMB7_UCSB_DEV

|

Module that interprets PROM commands and controls post-startup communication with EPROMs. More...

Entities | |

| SPI_CTRL_Arch | architecture |

Libraries | |

| ieee | |

| work | |

| unisim | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| ieee.numeric_std.all | |

| work.ucsb_types.all | |

| unisim.vcomponents.all | |

Ports | |

| CLK40 | in std_logic |

| 40 MHz clock input | |

| CLK2P5 | in std_logic |

| 2.5 MHz clock input | |

| RST | in std_logic |

| Soft reset signal. | |

| CMD_FIFO_IN | in std_logic_vector ( 15 downto 0 ) |

| SPI_CTRL command, clocked on CLK2P5. | |

| CMD_FIFO_WRITE_EN | in std_logic |

| Enable for SPI_CTRL command, clocked on CLK2P5. | |

| READBACK_FIFO_OUT | out std_logic_vector ( 15 downto 0 ) |

| Read output from readback FIFO, clocked on CLK2P5. | |

| READBACK_FIFO_READ_EN | in std_logic |

| Read enable for readback FIFO, clocked on CLK2P5. | |

| READ_BUSY | out std_logic |

| Indicates if a PROM read is in progress. | |

| CNFG_DATA_IN | in std_logic_vector ( 7 downto 4 ) |

| Data in from second EPROM. | |

| CNFG_DATA_OUT | out std_logic_vector ( 7 downto 4 ) |

| Data out to second EPROM. | |

| CNFG_DATA_DIR | out std_logic_vector ( 7 downto 4 ) |

| Tristate controller for second EPROM (1=to PROM) | |

| PROM_CS2_B | out std_logic |

| Chip select for second EPROM. | |

| RBK_WRD_CNT | out std_logic_vector ( 10 downto 0 ) |

| Number of words in readback FIFO. | |

| FSM_ENABLE | in std_logic |

| enable signal for finite state machine | |

| FSM_DISABLE | in std_logic |

| disable signal for finite state machine | |

| SPI_TIMER | out std_logic_vector ( 31 downto 0 ) |

| SPI timer register. | |

| SPI_STATUS | out std_logic_vector ( 15 downto 0 ) |

| SPI status register. | |

| DIAGOUT | out std_logic_vector ( 17 downto 0 ) |

| Debug signals. | |

Module that interprets PROM commands and controls post-startup communication with EPROMs.

supported PROM commands (sent with W 602C XXXX)

#Register Codes (for commands 0006 and 0012)

1.8.5

1.8.5