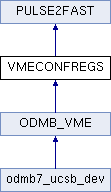

module for interacting with configuration and constant registers loaded from nonvolatile memory

More...

|

|

SLOWCLK | in |

| | 2.5 MHz clock input

|

|

CLK | in |

| | 40 MHz clock input

|

|

RST | in |

| | Soft reset signal.

|

|

DEVICE | in |

| | Indicates whether this is the selected VME device.

|

|

STROBE | in |

| | Indicates VME command is ready to be executed.

|

|

COMMAND | in ( 9 downto 0 ) |

| | VME command to be executed (x"4" & COMMAND & "00" is user-readable version)

|

|

WRITER | in |

| | Indicates if VME command is a read or write command.

|

|

DTACK | out |

| | Data acknowledge to be sent once command is initialized/executed.

|

|

INDATA | in ( 15 downto 0 ) |

| | Input data from VME backplane.

|

|

OUTDATA | out ( 15 downto 0 ) |

| | Output data to VME backplane.

|

|

LCT_L1A_DLY | out ( 5 downto 0 ) |

| | Configuration register controlling LCT delay in CALIBTRG.

|

|

CABLE_DLY | out range 0 to 1 |

| | CFG register controlling delay for DCFEB bound signals (L1A,L1A_MATCH,RESYNC,BC0) in top level.

|

|

OTMB_PUSH_DLY | out range 0 to 63 |

| | CFG register controlling delay between OTMBDAV and pushing to the FIFO in TRGCNTRL.

|

|

ALCT_PUSH_DLY | out range 0 to 63 |

| | CFG register controlling delay between ALCTDAV and pushing to the FIFO in TRGCNTRL.

|

|

BX_DLY | out range 0 to 4095 |

| | CFG register that would be used in counting bunch crossings in CAFIFO, but actually unused.

|

|

INJ_DLY | out ( 4 downto 0 ) |

| | CFG register controlling delay for calibration INJPULSE in CALIBTRG.

|

|

EXT_DLY | out ( 4 downto 0 ) |

| | CFG register controlling delay for calibration EXTPULSE in CALIBTRG.

|

|

CALLCT_DLY | out ( 3 downto 0 ) |

| | CFG register controlling delay for calibration LCT in CALIBTRG.

|

|

ODMB_ID | out ( 15 downto 0 ) |

| | CONST register storing the unique ODMB ID.

|

|

NWORDS_DUMMY | out ( 15 downto 0 ) |

| | CFG register controlling the number of words generated by dummy DCFEBs/ALCT/OTMB.

|

|

KILL | out ( NCFEB + 2 downto 1 ) |

| | CFG register controlling which boards (ALCT/OTMB/DCFEBs) should be ignored.

|

|

CRATEID | out ( 7 downto 0 ) |

| | CFG register withe crate ID, used by CONTROL_FSM in packet generation.

|

|

CHANGE_REG_DATA | in ( 15 downto 0 ) |

| | Signal to set new value for KILL register n case of auto-kill.

|

|

CHANGE_REG_INDEX | in range 0 to NREGS |

| | Signal to enable writing to CFG registers, only ever 7(for setting KILL) or NREGS(none)

|

|

SPI_CFG_UL_PULSE | in |

| | Signal from SPI_PORT to write CFG registers from PROM contents.

|

|

SPI_CONST_UL_PULSE | in |

| | Signal from SPI_PORT to write CONST registers from PROM contents.

|

|

SPI_REG_IN | in ( 15 downto 0 ) |

| | CFG or CONST register contents to be written, from SPI_PORT.

|

|

SPI_CFG_BUSY | in |

| | From SPI_PORT, indicates CFG register upload in progress.

|

|

SPI_CONST_BUSY | in |

| | From SPI_PORT, indicates CONST register upload in progress.

|

|

SPI_CFG_REG_WE | in range 0 to NREGS |

| | Write enable for each CFG register, from SPI_PORT.

|

|

SPI_CONST_REG_WE | in range 0 to NREGS |

| | Write enable for each CONST register, from SPI_PORT.

|

|

SPI_CFG_REGS | out cfg_regs_array |

| | Contents of CFG registers, used by SPI_PORT to save to PROM.

|

|

SPI_CONST_REGS | out cfg_regs_array |

| | Contents of CONST registers, used by SPI_PORT to save to PROM.

|

module for interacting with configuration and constant registers loaded from nonvolatile memory

Supported VME commands:

- W/R 40YZ read configuration register YZ/4

- R 4Y00 read constant register Y-1

- W/R 4FFC read constant register write mask (W disabled in most fw versions) The specific quantities stored in the configuration and constant registers are CFG register 0 (4000) LCT_L1A_DLY[5:0] LCT/L1A gap - 100 CFG register 1 (4004) OTMB_PUSH_DLY[5:0] L1A/OTMBDAV gap, read with "R 338C" CFG register 2 (4008) CABLE_DLY[0:0] delays L1A[_MATCH], RESYNC, BC0 by 25 ns CFG register 3 (400C) ALCT_DLY[5:0] L1A/ALCTDAV gap, read with "R 339C" CFG register 4 (4010) INJ_DLY[4:0] delay for INJPLS in units of 12.5 ns CFG register 5 (4014) EXT_DLY[4:0] delay for EXTPLS in units of 12.5 ns CFG reguster 6 (4018) CALLCT_DLY[3:0] delay for calibration LCT in units of 25 ns CFG register 7 (401C) KILL[9:1] for masking other boards (ALCT,TMB,7DCFEBs) CFG register 8 (4020) CRATEID[6:0] CFG register 9 (4024) Firmware ID, not writeable CFG register 10 (4028) NWORDS_DUMMY[15:0] number of words generated by simulated FE boards CFG register 11 (402C) BX_DLY[11:0] bunch crossing counter delay, unused CONST register 0 (4100) ODMB unique ID CONST register 1 (4200) Firmware version CONST register 2 (4300) Firmware build CONST register 3 (4400) Month/day firmware was synthesized CONST register 4 (4500) Year firmware was synthesized

1.8.5

1.8.5