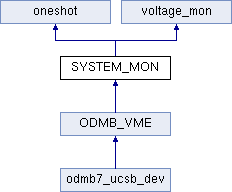

VME device controlling access to ODMB board monitoring (currents, voltages, temperature)

More...

|

|

OUTDATA | out ( 15 downto 0 ) |

| | Output data to VME backplane.

|

|

DTACK | out |

| | Data acknowledge to VME backplane.

|

|

ADC_CS_B | out ( 4 downto 0 ) |

| | SPI chip select to ADCs.

|

|

ADC_DIN | out |

| | SPI input to ADCs.

|

|

ADC_SCK | out |

| | SPI clock to ADCs.

|

|

ADC_DOUT | in |

| | SPI output from ADCs.

|

|

SLOWCLK | in |

| | 1.25 MHz clock

|

|

FASTCLK | in |

| | 40 MHz clock

|

|

RST | in |

| | Soft reset.

|

|

DEVICE | in |

| | Indicates if this is the selected VME device.

|

|

STROBE | in |

| | Indicates VME command ready.

|

|

COMMAND | in ( 9 downto 0 ) |

| | VME command.

|

|

WRITER | in |

| | Indicates if a command is read (1) or write (0)

|

|

VAUXP | in ( 15 downto 0 ) |

| | Current monitoring analog signals.

|

|

VAUXN | in ( 15 downto 0 ) |

| | Current monitoring analog signals.

|

VME device controlling access to ODMB board monitoring (currents, voltages, temperature)

Supported VME commands:

- R 7XY0 read SYSMON channel XY (see below) - current is result*10 channels 0 and 9 and result*5 for others

- W 73Y0 load data from ADC chip Y (chip 0-4)

- R 74Y0 read loaded ADC for channel Y (channels 1-8) - number is voltage/1000

#Sysmon channels 00 5V input current 01 3.3V current 02 3.3V optical current 03 3.3V clock current 04 3.6V PPIB current 05 2.5V current 06 1.2V MGT current 07 1.0V MGT current 08 0.95V core current 09 3.3V input current 10 1.8V current 11 1.8V VCC aux current 12 1.8V MGT current 13 1.8V VCCO current 14 1.8V VCCO0_65 current 15 1.8V clock current

The documentation for this class was generated from the following file:

- /homes/oshiro/odmb/firmware/odmb7_ucsb_dev/source/odmb_vme/system_mon.vhd

1.8.5

1.8.5