|

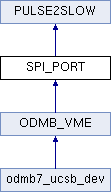

ODMB7_UCSB_DEV

|

VME device that acts as user interface to EPROM. More...

Entities | |

| SPI_PORT_Arch | architecture |

Libraries | |

| ieee | |

| work | |

| UNISIM | |

Use Clauses | |

| UNISIM.vcomponents.all | |

| work.Latches_Flipflops.all | |

| ieee.std_logic_1164.all | |

| ieee.numeric_std.all | |

| work.ucsb_types.all | |

Ports | |

| SLOWCLK | in std_logic |

| 2.5 MHz clock input | |

| CLK | in std_logic |

| 40 MHz clock input | |

| RST | in std_logic |

| Soft reset signal. | |

| DEVICE | in std_logic |

| Indicates whether this is the selected VME device. | |

| STROBE | in std_logic |

| Indicates VME command is ready to be executed. | |

| COMMAND | in std_logic_vector ( 9 downto 0 ) |

| VME command to be executed (x"6" & COMMAND & "00" is user-readable version) | |

| WRITER | in std_logic |

| Indicates if VME command is a read or write command. | |

| DTACK | out std_logic |

| Data acknowledge to be sent once command is initialized/executed. | |

| INDATA | in std_logic_vector ( 15 downto 0 ) |

| Input data from VME backplane. | |

| OUTDATA | out std_logic_vector ( 15 downto 0 ) |

| Output data to VME backplane. | |

| SPI_CFG_UL_PULSE | out std_logic |

| Signal to VMECONFREGS to write CFG registers read from PROM. | |

| SPI_CONST_UL_PULSE | out std_logic |

| Signal to VMECONFREGS to write const registers read from PROM. | |

| SPI_UL_REG | out std_logic_vector ( 15 downto 0 ) |

| Contents of CFG/const registers read from PROM. | |

| SPI_CFG_BUSY | out std_logic |

| Indicates CFG register upload in progress. | |

| SPI_CONST_BUSY | out std_logic |

| Indicated const register upload in progress. | |

| SPI_CFG_REG_WE | out integer range 0 to NREGS |

| Write enable for each CFG register. | |

| SPI_CONST_REG_WE | out integer range 0 to NREGS |

| Write enable for each const register. | |

| SPI_CFG_REGS | in cfg_regs_array |

| Contents of CFG registers to write to PROM. | |

| SPI_CONST_REGS | in cfg_regs_array |

| Contents of const registers to write PROM. | |

| SPI_RST | out std_logic |

| reset signal for SPI_CTRL state machine | |

| SPI_ENBL | out std_logic |

| signal to enable SPI_CTRL state machine | |

| SPI_DSBL | out std_logic |

| signal to disable SPI_CTRL state machine | |

| SPI_CMD_FIFO_WRITE_EN | out std_logic |

| Write enable to write command to PROM controller module. | |

| SPI_CMD_FIFO_IN | out std_logic_vector ( 15 downto 0 ) |

| Command to be written to PROM controller module. | |

| SPI_READBACK_FIFO_OUT | in std_logic_vector ( 15 downto 0 ) |

| Contents readback from PROM. | |

| SPI_READBACK_FIFO_READ_EN | out std_logic |

| Read enable to progress through contents readback from PROM. | |

| SPI_READ_BUSY | in std_logic |

| Indicates a PROM read in progress. | |

| SPI_RBK_WRD_CNT | in std_logic_vector ( 10 downto 0 ) |

| Number of words in SPI readback FIFO. | |

| SPI_TIMER | in std_logic_vector ( 31 downto 0 ) |

| SPI timer register from SPI_CTRL. | |

| SPI_STATUS | in std_logic_vector ( 15 downto 0 ) |

| SPI status register from SPI_CTRL. | |

| DIAGOUT | out std_logic_vector ( 17 downto 0 ) |

| Debug signals. | |

VME device that acts as user interface to EPROM.

Replaces BPI_PORT and BPI_CFG_CONTROLLER modules from legacy ODMB firmware. Supported VME commands:

1.8.5

1.8.5