|

|

FASTCLK | in |

| | 40 MHz clock

|

|

SLOWCLK | in |

| | 2.5 MHz clock

|

|

GAP | in |

| | Geographical address parity, must match GA.

|

|

GA | in ( 4 downto 0 ) |

| | Crate geographical address, checked against command.

|

|

ADR | in ( 23 downto 1 ) |

| | VME ADDR (command), must match GA.

|

|

AM | in ( 5 downto 0 ) |

| | VME address modifier, must be 111X10 or 111X01.

|

|

AS | in |

| | Address strobe, indicates AM and ADR can be read.

|

|

DS0 | in |

| | Data strobe, indicates data is ready.

|

|

DS1 | in |

| | Data strobe, indicates data is ready.

|

|

LWORD | in |

| | VME word length, must be 1.

|

|

WRITER | in |

| | VME read(1)/write(0), only used for debug.

|

|

IACK | in |

| | VME Interrupt acknowledge bar, must be 1.

|

|

BERR | in |

| | VME bus error bar, unused.

|

|

SYSFAIL | in |

| | VME system fail bar, must be 1.

|

|

DEVICE | out ( 9 downto 0 ) |

| | Output to select VME device for command.

|

|

STROBE | out |

| | Signal to initiate interpretation of VME command.

|

|

COMMAND | out ( 9 downto 0 ) |

| | VME command output (subset of VME ADDR)

|

|

ADRS | out ( 17 downto 2 ) |

| | Output to select VME device to multiplex to VME.

|

|

TOVME_B | out |

| | Selects VME input/output direction.

|

|

DOE_B | out |

| | VME output enable to ODMB ICs.

|

|

DIAGOUT | out ( 17 downto 0 ) |

| | Debug signals.

|

|

LED | out ( 2 downto 0 ) |

| | Debug signals.

|

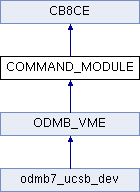

module that interprets VME commands for modules in ODMB VME

1.8.5

1.8.5