|

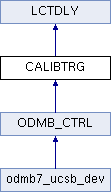

ODMB7_UCSB_DEV

|

Entities | |

| CALIBTRG_arch | architecture |

Libraries | |

| ieee | |

| work | |

| UNISIM | |

Use Clauses | |

| UNISIM.vcomponents.all | |

| ieee.std_logic_1164.all | |

| ieee.std_logic_arith.all | |

| work.Latches_Flipflops.all | |

Ports | |

| CMSCLK | in std_logic |

| CLK80 | in std_logic |

| RST | in std_logic |

| PLSINJEN | in std_logic |

| CCBPLS | in std_logic |

| CCBINJ | in std_logic |

| FPLS | in std_logic |

| FINJ | in std_logic |

| FPED | in std_logic |

| PRELCT | in std_logic |

| PREGTRG | in std_logic |

| INJ_DLY | in std_logic_vector ( 4 downto 0 ) |

| EXT_DLY | in std_logic_vector ( 4 downto 0 ) |

| CALLCT_DLY | in std_logic_vector ( 3 downto 0 ) |

| LCT_L1A_DLY | in std_logic_vector ( 5 downto 0 ) |

| RNDMPLS | in std_logic |

| RNDMGTRG | in std_logic |

| PEDESTAL | out std_logic |

| CAL_GTRG | out std_logic |

| CALLCT | out std_logic |

| INJBACK | out std_logic |

| PLSBACK | out std_logic |

| LCTRQST | out std_logic |

| INJPLS | out std_logic |

1.8.5

1.8.5