|

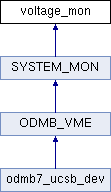

ODMB7_UCSB_DEV

|

module implementing SPI interface to MAX1271B chips More...

Entities | |

| voltage_mon_arch | architecture |

Libraries | |

| IEEE | |

| unisim | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| ieee.numeric_std.all | |

| ieee.std_logic_misc.all | |

| ieee.std_logic_unsigned.all | |

| unisim.vcomponents.all | |

Ports | |

| CLK | in std_logic |

| 1.25MHz clock | |

| CS | out std_logic |

| SPI chip select to ADCs. | |

| DIN | out std_logic |

| SPI input to ADCs. | |

| SCK | out std_logic |

| SPI clock to ADCs. | |

| DOUT | in std_logic |

| SPI output from ADCs. | |

| DVOUT | out std_logic |

| output data to fw valid | |

| DATADONE | out std_logic |

| indicates data retrieved from ADCs | |

| DATA | out std_logic_vector ( 11 downto 0 ) |

| output data to fw | |

| DATAVALIDCNTR | out std_logic_vector ( 7 downto 0 ) |

| counts bits of data received; debug signal | |

| CURRENTCHANNELOUT | out std_logic_vector ( 2 downto 0 ) |

| current channel being read; debug signal | |

| CTRLSEQDONE | out std_logic |

| indicates control sequence has been sent; debug signal | |

| startchannelvalid | in std_logic |

| begins an ADC read | |

module implementing SPI interface to MAX1271B chips

1.8.5

1.8.5