|

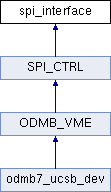

ODMB7_UCSB_DEV

|

Module that directly generates SPI signals for post-startup communication with EPROMS. More...

Entities | |

| behavioral | architecture |

Libraries | |

| ieee | |

| UNISIM | |

Use Clauses | |

| ieee.std_logic_1164.all | |

| ieee.std_logic_unsigned.all | |

| ieee.numeric_std.all | |

| UNISIM.vcomponents.all | |

| work.ucsb_types.all | |

Ports | |

| CLK | in std_logic |

| 40 MHz clock input | |

| RST | in std_logic |

| Soft reset signal. | |

| WRITE_FIFO_INPUT | in std_logic_vector ( 15 downto 0 ) |

| Data to write to programming FIFO. | |

| WRITE_FIFO_WRITE_ENABLE | in std_logic |

| Write enable for programming FIFO. | |

| START_ADDRESS | in std_logic_vector ( 31 downto 0 ) |

| Address to start operation. Only bottom 3 bytes used. | |

| START_ADDRESS_VALID | in std_logic |

| Signal to load address. | |

| WRITE_NWORDS | in unsigned ( 11 downto 0 ) |

| Number of words to program. | |

| START_WRITE | in std_logic |

| Signal to begin programming. | |

| OUT_WRITE_DONE | out std_logic |

| '1' unless program in progress | |

| READ_NWORDS | in unsigned ( 11 downto 0 ) |

| Number of words to read. | |

| START_READ | in std_logic |

| Signal to begin read. | |

| OUT_READ_DONE | out std_logic |

| '1' unless read in progress | |

| START_ERASE | in std_logic |

| Signal to begin erase (1 sector) | |

| OUT_ERASE_DONE | out std_logic |

| '1' unless erase in progress | |

| START_UNLOCK | in std_logic |

| Signal to erase nonvolatile lock bits on all sectors. | |

| OUT_UNLOCK_DONE | out std_logic |

| '1' unless erase nonvolatile lock bits in progress | |

| START_LOCK | in std_logic_vector ( 1 downto 0 ) |

| Signal to write lock bit - MSB is 0 for nonvolatile 1 for volatile. | |

| OUT_LOCK_DONE | out std_logic |

| '1' unless write lock bits in progress | |

| START_READ_LOCK | in std_logic_vector ( 1 downto 0 ) |

| Signal to read lock bit - MSB is 0 for nonvolatile 1 for volatile. | |

| OUT_READ_LOCK_DONE | out std_logic |

| '1' unless read lock bits in progress | |

| START_READ_ID | in std_logic |

| Signal to read PROM ID. | |

| OUT_READ_ID_DONE | out std_logic |

| '1' unless read ID in progress | |

| START_CLEAR_STATUS | in std_logic |

| Signal to clear status flag register. | |

| OUT_CLEAR_STATUS_DONE | out std_logic |

| '1' unless clear status flag in progress | |

| START_WRITE_REGISTER | in std_logic_vector ( 3 downto 0 ) |

| Signal to write register, bit 3 indicates start and bits 2:0 indicate register. | |

| OUT_WRITE_REGISTER_DONE | out std_logic |

| '1' unless write register in progress | |

| REGISTER_CONTENTS | in std_logic_vector ( 15 downto 0 ) |

| Register contents to be written with write register commands. | |

| START_READ_REGISTER | in std_logic_vector ( 3 downto 0 ) |

| Signal to start read register, when nonzero, indicates register. | |

| OUT_READ_REGISTER_DONE | out std_logic |

| '1' unless read register in progress | |

| OUT_REGISTER | out std_logic_vector ( 7 downto 0 ) |

| Contents of register read out. | |

| OUT_REGISTER_WE | out std_logic |

| Write enable for register. | |

| START_CUSTOM | in std_logic_vector ( 11 downto 0 ) |

| Signal to start custom command where (11 downto 1) are number of bits to send and (0) is start. | |

| CUSTOM_WORDS_TO_READ | in std_logic_vector ( 15 downto 0 ) |

| Number of bytes to read from custom command; should be set before START_CUSTOM(0) | |

| OUT_CUSTOM_DONE | out std_logic |

| '1' unless custom SPI command in progress | |

| OUT_READ_DATA | out std_logic_vector ( 15 downto 0 ) |

| Data read out from PROM. | |

| OUT_READ_DATA_VALID | out std_logic |

| Indicates when data from PROM is valid. | |

| PROM_SELECT | in std_logic |

| Selector for which PROM is used (0=primary, 1=secondary) | |

| CNFG_DATA_IN | in std_logic_vector ( 7 downto 4 ) |

| Data in from second EPROM. | |

| CNFG_DATA_OUT | out std_logic_vector ( 7 downto 4 ) |

| Data out to second EPROM. | |

| CNFG_DATA_DIR | out std_logic_vector ( 7 downto 4 ) |

| Tristate controller for second EPROM (1=to PROM) | |

| PROM_CS2_B | out std_logic |

| Chip select for second EPROM. | |

| DIAGOUT | out std_logic_vector ( 17 downto 0 ) |

| Debug signals. | |

Module that directly generates SPI signals for post-startup communication with EPROMS.

1.8.5

1.8.5