## OSLO !

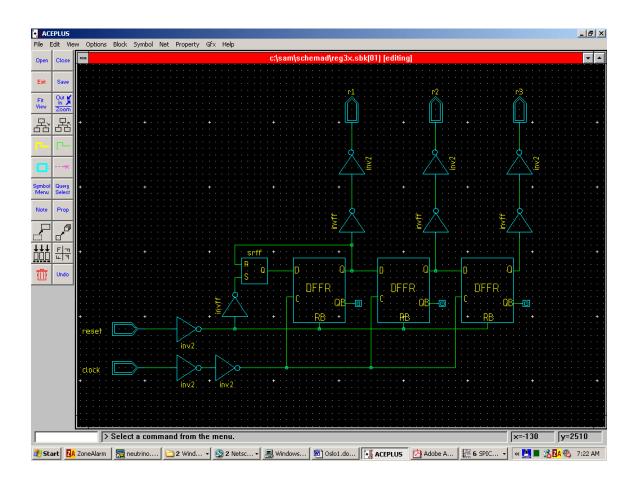

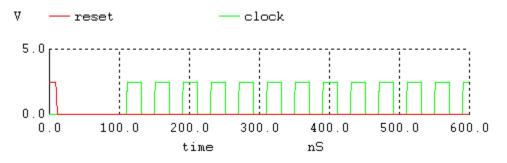

Orientation with Win-Spice 1.4.0 to simulate a 4 bit ripple counter for use in the x ray event counter. Once the schematic has been created one needs to generate a netlist using "netgen.bat" which must point the the saved schematic file (must edit two lines in the bat file). The input file must be edited to specify the stimuli (input signal), filename.txt in the WinSpice\input folder. Exicute the netgen bat file to generate a netlist, check to see how it looks. Edit the simulate.txt file to point at the 4 required files to carry out the Spice application. Use the "plot x y z etc" command in the spice command line file to view the resulting signals.

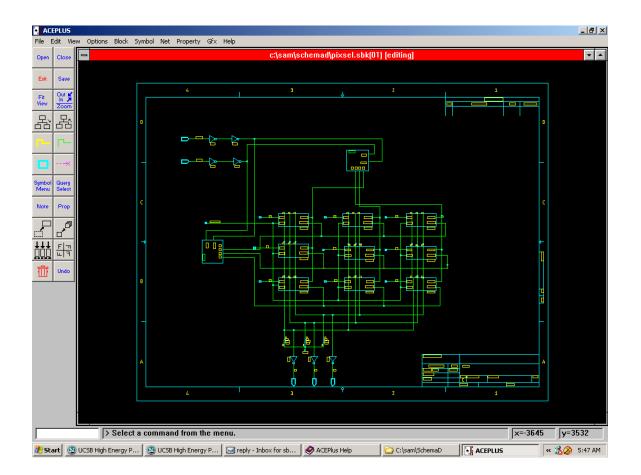

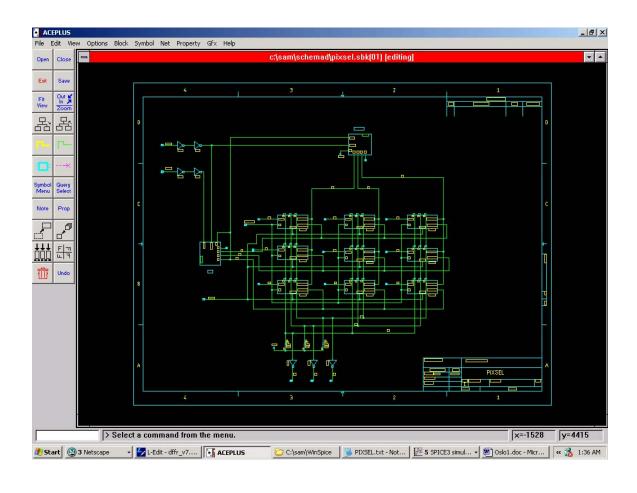

The digital readout of 18 bit ripple counters from a 4x4 pixel array will use a row/columb selector with a multiplexer/shift register. Pixel register 01 will be latched into an 18 bit shift register and shifted followed by pixel 02 finishing up with pixel 16. The shift rate must be 130 Mhz. A 3 stage shift register with a bit seed will be used to address the separate pixels.

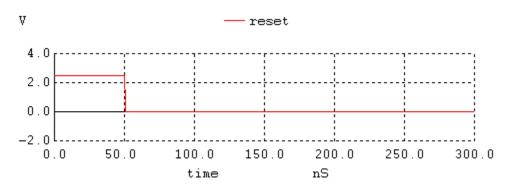

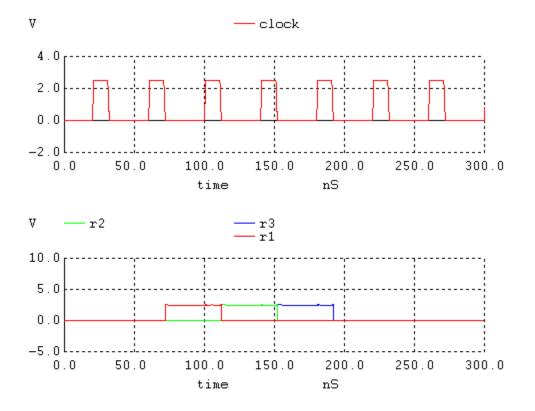

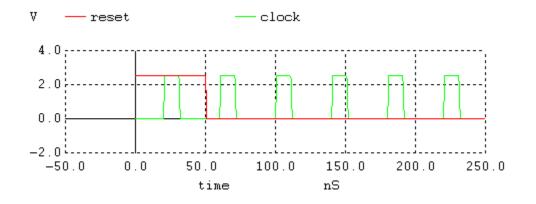

A Feedback FB input was added to 3bit columb and row shift registers and r3 from row register is used as the clock for the columb register, r3 from the row register is also fed back to the

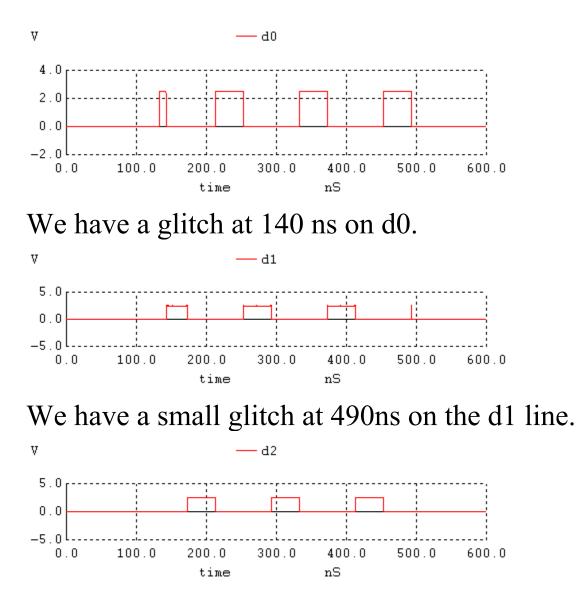

## Feedback input of the same register with results shown below following simulation.

Reset and clear are the same above.

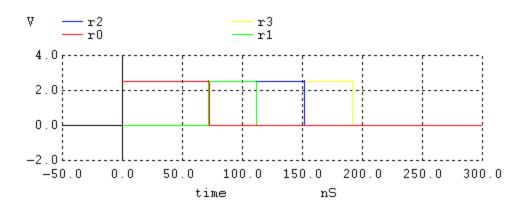

The Pixel readout is shown below decoded;

| 2 | 2 | 2 |

|---|---|---|

| 4 | 4 | 4 |

| 1 | 1 | 1 |

The Test Inputs used in the Spice simulation for the 3x3 pixel array decoder was generated with the test file below;

\*\*\*\*\* test1 input deck \*\*\*\*\*\*\*

vreset reset 0 pulse 2.5 0 10n 1n 1n 1 2 vclock clock 0 pulse 0 2.5 110n 1n 1n 20n 40ns vclear clear 0 pulse 2.5 0 10n 1n 1n 1 2 vcount\_en count\_en 0 pulse 0 2.5 25n 1n 1n 80ns 1 vp0 p0 0 pulse 0 2.5 30n 1n 1n 10n 20n vp1 p1 0 pulse 0 2.5 30n 1n 1n 5n 10n vp2 p2 0 pulse 0 2.5 30n 1n 1n 15n 30n vp3 p3 0 pulse 0 2.5 30n 1n 1n 10n 20n vp4 p4 0 pulse 0 2.5 30n 1n 1n 5n 10n vp5 p5 0 pulse 0 2.5 30n 1n 1n 15n 30n vp6 p6 0 pulse 0 2.5 30n 1n 1n 10n 20n vp7 p7 0 pulse 0 2.5 30n 1n 1n 5n 10n vp8 p8 0 pulse 0 2.5 30n 1n 1n 5n 30n

.control

## tran 1ns 600n

## .endc

| <br> | <br> |

|------|------|

| <mark>↓/L-Edit-[Cell0 latch.tdb]</mark> |               | _ D ×            |

|-----------------------------------------|---------------|------------------|

| (1) (1) (1) (1) (1) (1) (1) (1) (1) (1) | .80 Microns 💌 | 느먹스              |

|                                         | 1 🖽 er 🔛 🔖    | 🥦 🎇 🖉            |

| MET2                                    |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         | 8             |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               |                  |

|                                         |               | Mode: Drawing // |

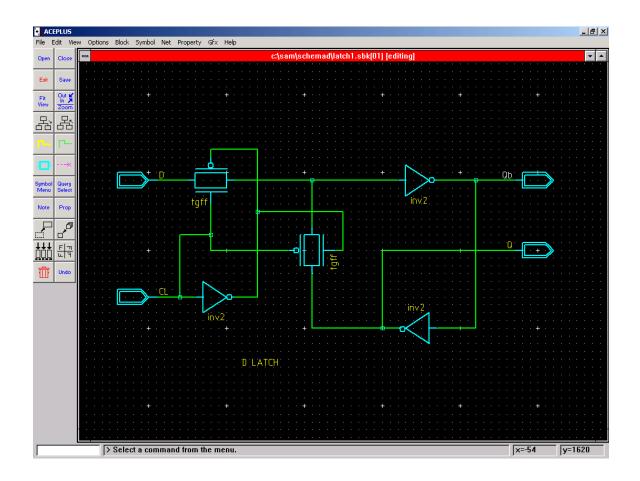

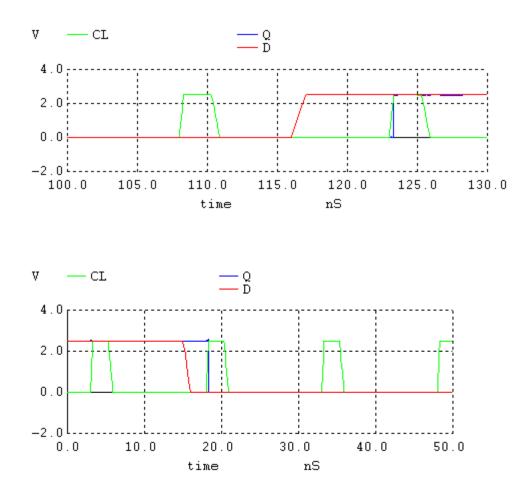

This is the layout on Si using the Oester Microsystems process. From left to right we have a SPDT transmission gate followed by three inverters with appropriate interconnects.

| <mark>∽k-Edit - [Cell0 latch.tdb*]</mark><br>중 File Edit View Draw Cell Setup Tools Window Help |                                                           |               |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|

|                                                                                                 | 🔻 💕 🖻 🖳 🬧 🕴 76.35 : 47.50 🛛 Mi                            |               |

|                                                                                                 |                                                           |               |

|                                                                                                 |                                                           |               |

| MET2                                                                                            |                                                           |               |

|                                                                                                 | 💖 DRC Progress                                            |               |

|                                                                                                 | Cell: Cell0                                               |               |

|                                                                                                 | Elapsed time: 6 sec.                                      |               |

|                                                                                                 | Estimated time remaining: 0 sec.                          |               |

|                                                                                                 | 6 geometry flags checked                                  |               |

|                                                                                                 | 127 rules out of 127 completed (100%)                     |               |

|                                                                                                 | Done                                                      |               |

|                                                                                                 | 56 DRC errors found                                       |               |

|                                                                                                 | Rule Name                                                 | Errors        |

|                                                                                                 | Self-intersecting polygons and wires<br>3.1.1 NTUB width. | 18<br>2       |

|                                                                                                 | 3.1.3 NTUB notch. (xck 3.1.2)<br>3.3.2 DIFF spacing.      | 2             |

|                                                                                                 | 3.4.1 POLY1 width.                                        | 3             |

|                                                                                                 | 3.4.2 POLY1 spacing.<br>3.4.3 POLY1 notch. (xck 3.4.2)    | 4             |

|                                                                                                 | 3.9.1 CONT width.                                         | 2             |

|                                                                                                 | 3.10.2 MET1 spacing.                                      | 15            |

|                                                                                                 |                                                           |               |

|                                                                                                 | 1                                                         |               |

|                                                                                                 | When DRC completes                                        |               |

| Polygons with more than 199 vertices [0]                                                        | Show Summary Report                                       |               |

| └── 🖉 🏈 Wires with more than 200 vertices [0]                                                   |                                                           |               |

| ⊕ - ☐ If Self-intersecting polygons and wires [18] These objects are ignored                    | Close                                                     |               |

| ·····································                                                           |                                                           |               |

| ⊕ - □ 🔗 3.1.3 NTUB notch. (xck 3.1.2) [2] < 5 Microns                                           |                                                           |               |

| −□                                                                                              |                                                           |               |

|                                                                                                 |                                                           |               |

| A 324 (adr) NTHB without FIMP. Generate AG. FIMPLINI                                            |                                                           |               |

|                                                                                                 | 20 December 2010                                          | Mode: Drawing |

The Latch has 56 DRC errors so no simulation can proceed until they are taken care of.