• Electrical and optical hybrids not burnt-in prior to arrival at UCSB/FNAL

→ No burn-in program for foreseen before full production

- Rod components currently scheduled to arrive much later than module components (~6 month)

- → Large supply of finished modules prior to rod construction

- → Minimal information of long-term stability of most components

- Necessitates burn-in of a fraction of modules prior to rod construction Sample each construction jig periodically

- Vienna cold box and rod burn-in only systems viable for such a program

- → Vienna cold box software already tested and written

UCSB Short-term Testing Plan

- Characterize hybrid (+PA) on arrival

- $\rightarrow$  Basic functionality and deep test (ARC)

- Specific bad channel requirements for hybrid (+PA)

- Re-characterize module on completion of construction

- $\rightarrow$  Basic functionality, deep test, IV curves (ARC)

- Different bad channel requirement for module

- Vienna cold box test fraction of modules (DAQ)

- $\rightarrow$  Acts as ~24 hour module burn-in

- Scaled bad channel requirements for change in gain, grounding, etc.

- Identifies mechanical/bond/electrical weaknesses prior to production of large number of modules

- Reduces reworking of rod/retrofitting of modules

- Make bad channel requirements specific to component type tested

- → (hybrid, hybrid+PA, module)

- Remove/loosen relative percentage/sigma requirements

- Tighten/add fixed requirements

- Motivate requirements on silicon tracker performance

- Increase minimum noise test

- → Fractional requirements too wide to discern saturated/dead FE preamplifier

- Replace fractional pedestal requirements with  $|P_i-P_{chip}| < P_{cut}$

- $\rightarrow$  P<sub>cut</sub> motivated by decrease in dynamic range of channel

- Special requirements on chip edges if necessary

- Remove current pulse shape requirements

Include rise-time/fall-time/peak-time requirement

- Replace pulse shape with gain measurement

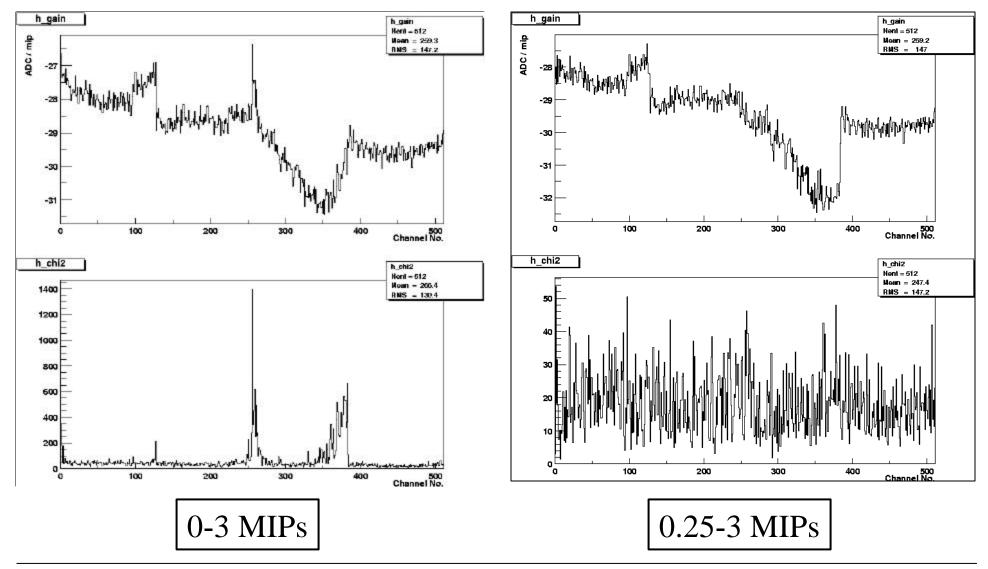

- → Measure pulse heights at 6-13 calibration injection setting between 0-3 MIPs and fit

- → Require gain between  $G_{low}$  and  $G_{high}$

- Gain uniformity specification

Calibration circuit may not be uniform

- → Require  $\chi^2 < \chi^2_{cut}$  ( $\chi^2$  based on noise measurement)

- Finds non-linear charge response and gain non-uniformities

- Should be relatively simple to include in ARC software

- See following example

## Hybrid Gain Measurement(1)

US CMS Meeting 12/3/2002

Proposal of UCSB Short-term Testing Program

Anthony Affolder

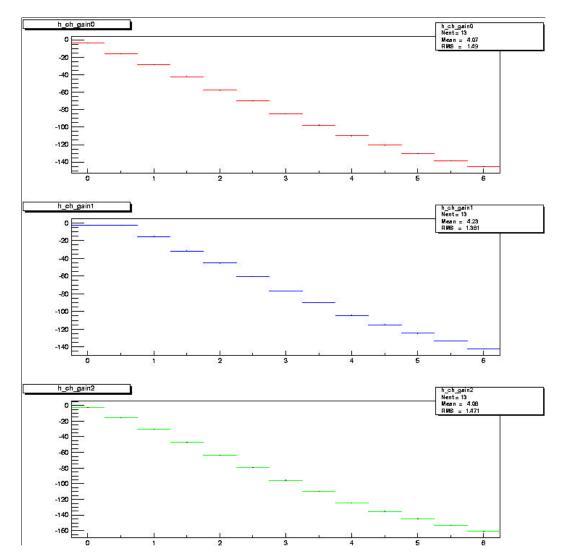

- Three channels' pulse height vs. MIP injected

- → First 'regular'

- $\rightarrow$  Second 1<sup>st</sup> channel of chip 3

- $\rightarrow$  Third 63<sup>th</sup> channel of chip 3

- Gain non-uniform and bad  $\chi^2$  if 0 MIP point included for chip 3

- Improved if 0 MIP excluded

- Mostly likely calibration circuit non-uniformities

- Add pipeline capacitor pedestal/noise requirement

- → Widen relative to channel requirement according to decreased statistics

- Add pipeline column pedestal/noise requirement

- Remove bad capacitors/columns from channel pedestal/noise calculation

- Grade ladders by fraction of bad capacitors

- → Bad channel=190 capacitors

- → Bad column=128 capacitors

- Treat chip edges differently (if necessary)

- DAQ with 10 hybrid channels

- LV/HV power supplies

→ Reusable for rod burn-in

- Vienna cold box

- DI/O PC board

- 1.5 kW chiller

- Module carriers